AMD的CCD+IOD Chiplet设计,就像是一场精心策划的「芯片盛宴」,将多个芯片模块组合在一起,打造出强大的处理器。 然而,最近却传出了一些令人担忧的消息:锐龙9000系列处理器出现了核心之间延迟骤然加大的情况,最高可达200纳秒左右!这就好比一场盛宴,菜肴虽然美味,但上菜速度却慢得让人抓狂。

究竟是什么原因导致了这种延迟的「灾难」? 经过一番调查,我们发现问题就出在AMD的微代码上。微代码就像是一套操作系统,它负责协调处理器内部各个模块之间的工作。而之前的微代码版本,似乎在处理核心之间的数据传输时,出现了「迷路」的情况,导致延迟大幅增加。

好在,AMD及时发布了新的AGESA 1.2.0.1版微代码,并迅速得到主板厂商的支持。 这就好比一位经验丰富的「领航员」,及时修正了航线,让数据传输更加顺畅。

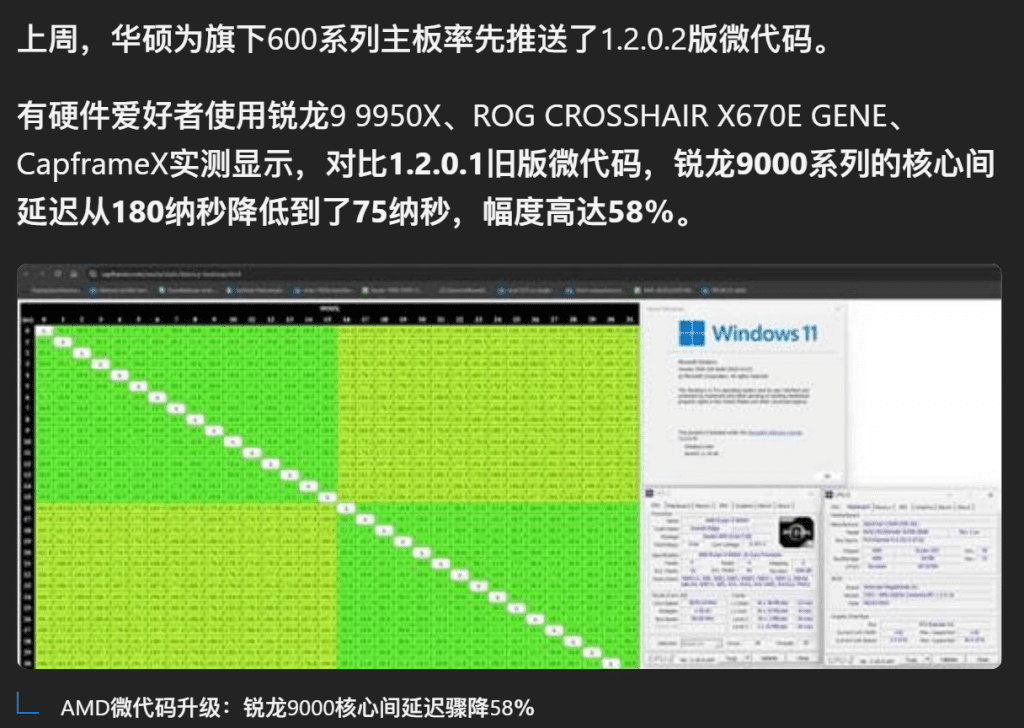

实测结果显示,升级到1.2.0.1版微代码后,锐龙9000系列的核心间延迟从180纳秒降低到了75纳秒,降幅高达58%! 这就像是一场「延迟大作战」,最终以AMD的胜利告终。

这次微代码升级,不仅解决了延迟问题,还提升了锐龙9000系列处理器的性能表现。 我们可以期待,AMD的「芯片盛宴」将更加精彩!

参考文献:

- AMD官网

- 华硕官网

- CapframeX官网